В этой статье мы рассмотрим технологию FinFET, ее использование, применение, а также преимущества и недостатки, которые у нее имеются по сравнению с MOSFET технологией.

![]() Время чтения: 10 минут

Время чтения: 10 минут

Что такое FinFET?

FinFET – это транзисторы, выполненные по определенной технологии. И будучи транзистором, он может выполнять функции как усилителя, так и ключа. По Fin-технологии изготавливаются микрочипы, используемые в домашних компьютерах, ноутбуках, планшетах, смартфонах, различных носимых устройствах, сетевых устройствах, автомобильной промышленности, а также во многих других.

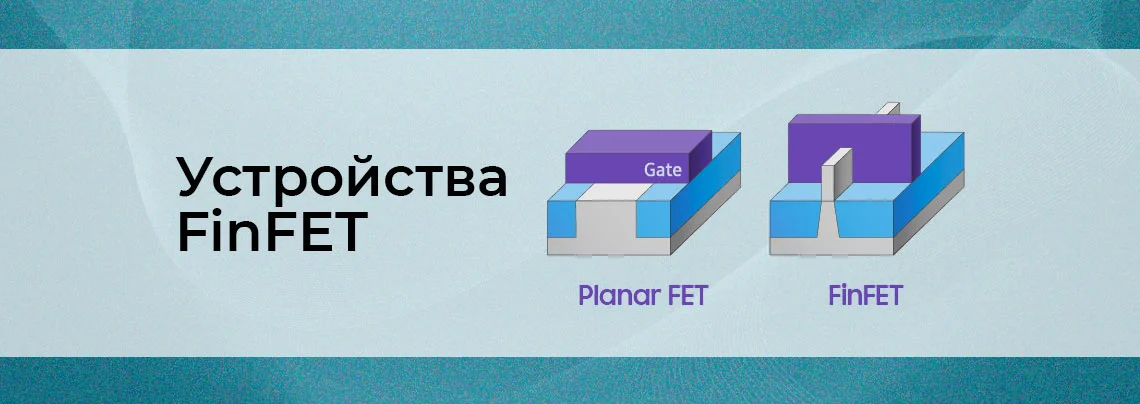

В основе конструкции транзистора лежит кремниевое ребро, которое образует основу его корпуса. Поэтому своё название - Fin (англ. ребро, плавник) технология получила как раз из-за формы. Управление проводимостью канала осуществляется электрическим полем, поэтому FinFET транзисторы также являются полевыми.

Если ранее полупроводниковые устройства изготавливались планарной (плоской или двумерной) конструкции, то выступающее над поверхностью подложки ребро Fin-транзисторов переводит их в третье измерение. Поэтому их также называют 3D или трехмерными транзисторами.

Назначение FinFET устройств

Есть целый ряд причин, почему выбор устройств на основе FinFET технологии предпочтительнее, чем традиционных MOSFET-устройств, существующие уже многие годы. Основная причина – необходимость увеличения вычислительной мощности. Для достижения этого требуется больше транзисторов, что ведет к увеличению размеров микросхемы. Однако с практической точки зрения важно сохранить площадь микрочипов примерно на том же существующем уровне. Поэтому необходимо увеличить вычислительную плотность микросхемы, то есть разместить большее число полупроводников на единицу площади.

Одним из способов увеличения вычислительной мощности является уменьшение размера единичного транзистора. Однако это сопровождается сближением стока с истоком, что ведет к уменьшению способности затвора управлять потоком электрического тока в области канала.

Из-за своей конструкции планарные МОП-транзисторы демонстрируют различные нежелательные эффекты короткого канала. Так, например, уменьшение длины затвора (LGATE) ниже 90 нм приводит к значительному росту тока утечки, а при достижении 28 нм утечка является чрезмерной настолько, что делает транзистор бесполезным. Таким образом, основной задачей, при уменьшении длины затвора между полупроводниками, является снижение тока утечки в запертом состоянии.

Другим способом увеличения вычислительной мощности является – применение новейших материалов, при изготовлении микрочипов. Однако такой способ требует значительных затрат, что может оказаться экономически неоправданным.

Благодаря своему объемному исполнению FinFET устройства имеют хорошие характеристики при коротком канале. Также, по сравнению с классическими MOSFET элементами, они имеют значительно меньшее время переключения и более высокую плотность тока.

Размеры FET-элементов

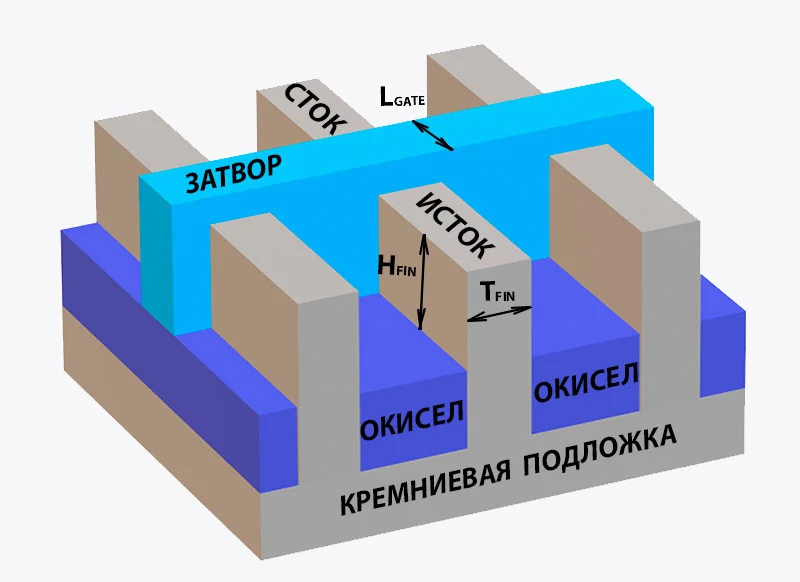

Конструктивно Fin-ячейки имеют узкий вертикальный токопроводящий канал. Его размеры сопоставимы с длиной волны де Бройля, что создает размерный эффект, а также вызывает квантование энергии носителей заряда (электронов). Поэтому при их конструировании требуется учитывать не только линейные размеры канала, но и их соотношение.

Толщина ребер канала является решающим параметром, поскольку она влияет на поведение короткого канала и подпороговый размах. Подпороговый размах характеризует изменение логарифма напряжения на затворе на декаду (порядок) тока стока. Этот показатель определяет эффективность работы транзистора.

Технология FinFET позволила улучшить рабочие характеристики, сохранить, а в перспективе даже увеличить плотность размещения транзисторов. Так как определяющей характеристикой считается контактная площадь между затвором и рабочим каналом, то размеры ребра являются ключевыми для оценки характеристик полупроводниковой ячейки.

Первым показателем, характеризующим ячейку, является минимальный размер транзистора. Он оценивается длиной периметра соприкосновения канала с затвором:

WMIN = 2 ∙ HFIN + TFIN

При этом общая ширина ячейки будет завесить от числа параллельных каналов (n):

W = n ∙ WMIN

Другим учитываемым показателем является эффективная ширина (WEFF). Она позволяет учесть в расчетах межреберное расстояние (PFIN):

WEFF = (2 ∙ HFIN + TFIN) / PFIN

Преимущества

По сравнению с планарной конструкцией, FinFET микрочипы обладают такими ключевыми преимуществами, как:

- лучший контроль над работой канала;

- значительное подавление эффектов короткого канала;

- низкий ток утечки в статическом режиме;

- высокая скорость переключения;

- более высокий ток канала (на единицу площади);

- низкое напряжение открытия;

- низкое энергопотребление.

Недостатки

Любое современное технологическое решение имеет не только преимущества, но и недостатки. Fin-устройства также не избежали этой участи. К их недостаткам можно отнести:

- сложность динамического контроля за пороговым напряжением затвора (VGE(th));

- квантование размеров (Размеры устройства обязательно должны быть кратными целым ребрам, а дробные пропорции недопустимы);

- более высокие паразитные характеристики (благодаря трехмерному профилю);

- очень высокие емкостные характеристики;

- образование углового эффекта (когда электрическое поле на узкой грани значительно выше чем на широкой боковой);

- высокая стоимость изготовления.

Эволюция FET устройств

Основой современной электроники являются МОП-транзисторы. За многие десятилетия своего существования технология CMOS добилась значительных успехов. В первую очередь это произошло за счет совершенствования архитектуры, а также материалов, используемых в производстве.

Большим скачком стало внедрение в 2000 году технологии атомно-слоевого осаждения ALD (Atomic Layer Deposition), а также применение High-k диэлектриков. Эти факторы позволили перешагнуть 140 нм порог.

Однако уже менее чем за 10 лет был достигнут 30-нанометровый рубеж ставший пределом планарной конструкции MOSFET-устройств. Дальнейшая миниатюризация полупроводниковых ячеек вела к значительному росту тока утечки и ложным срабатываниям из-за явления квантового туннелирования.

Очевидным решением стал переход к 3D структурам, позволившим продолжить дальнейшее уплотнение. И уже 2012 год ознаменовался появлением на свет первого коммерческого 22-нм FinFET микрочипа. Последующие усовершенствования архитектуры позволили значительно повысить производительность устройств, а за счет увеличения высоты ребер – добиться более высокого управляющего тока.

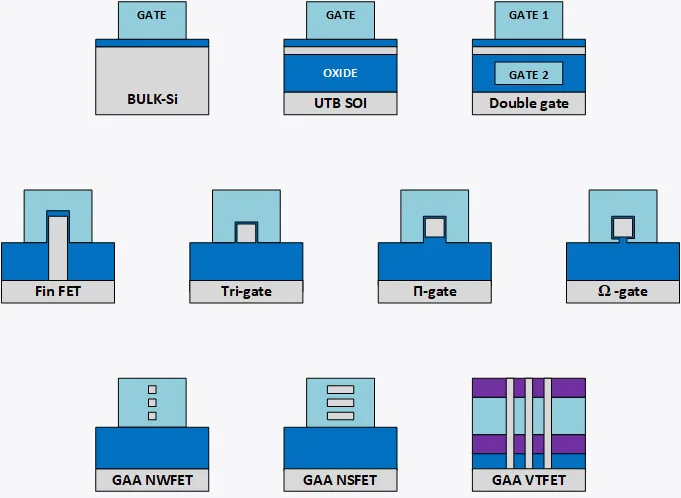

На рисунке представлена эволюция полупроводниковых структур. При их большом разнообразии двухзатворные и трехзатворные конструкции получили значительное распространение из-за их несложной конструкции и простоты в изготовлении.

Конструкция GAA (Gate-all-Around) хоть и была предложена еще до изобретения Fin, однако последняя была более удобна для внедрения в производство.

Что нас ждет в будущем?

Технология FinFET не имеет видимых перспектив развития за пределами 5-нанометрового рубежа. В первую очередь это связано с отсутствием достаточного электростатического контроля. Поэтому дальнейшая миниатюризация потребует новых архитектурных решений при создании полупроводниковых ячеек.

Однако по мере развития технологических линий некоторые компании, по экономическим соображениям, уже приняли решение временно остаться на том же уровне производства дальше. Другие же, в силу характера своих производственных процессов, вынуждены продолжить внедрение новых технологических решений.

Уже сейчас ясно, что для сильно масштабируемых технологических узлов GAA-технология является основным преемником FinFET. Однако структура Gate-all-Around имеет серьёзный недостаток – она создает значительную емкостную связь между затвором и каналом. Поэтому в действительности проблемы с GAAFET больше связаны с производством, чем с величиной тока утечки. Но успешная реализация GAA-ячеек даст запас еще на десяток лет, которые будут направлены на поиск и разработку новых решений по дальнейшей миниатюризации.

В настоящее время только две компании, тайваньская TSMC и южнокорейская Samsung, работают с технологиями 7 нм и ниже. Причем уже летом 2022 года Samsung начал массовое производство 3-нанометровых микрочипов, выполненных по технологии GAA NSFET.

В 2021 году Intel, анонсировал планы выхода к 2024 году на 2 нм, под маркой Intel 20A (20 ангстрем). Для этого компания реализует RibbonFET конструкцию полупроводниковых ключей, значительно схожую с NSFET, а также существенно изменит архитектуру микросхем.

В общем, в ближайшем будущем нас ждут «живые» тесты 3 нм микрочипов Samsung, новая архитектура от Intel, а также другие прорывные решения в эволюции полупроводников.

Инновации в технологии CMOS были достигнуты за счет непрерывного уменьшения размеров с целью повышения вычислительной плотности. В результате это привело к увеличению производительности и снижения общего энергопотребления устройств. Однако непрерывная миниатюризация привела к проявлению негативных короткоканальных эффектов, а также проблемам в управлении работой канала.

Планарная конструкция MOSFET не позволила масштабироваться бесконечно, столкнувшись с серьезными проблемами в нанометровом пространстве. Так, при длине затвора менее 30 нм оксид под ним уже не справляется с изолированием и возникают проблемы с управлением каналом. Даже при использовании под затвором идеального диэлектрика с нулевой толщиной управление будет возможно только в области непосредственно под самим затвором. При этом током утечки управлять уже будет невозможно, поскольку он находится слишком на большом расстоянии от затвора. Всё это ведет к значительному росту выходного тока, а также ухудшению подпорогового размаха и затруднением выключение транзистора.

Устранение тока утечки является основным средством улучшения электростатического контроля. Один из способов сделать это - использовать структуру с несколькими затворами. Такая конструкция позволяет удерживать ток утечки в центре канала, а уменьшение толщины этого канала снижает величину тока.

FinFET-конструкция лучше блокирует эффекты короткого канала чем планарная, а также позволяет продолжить дальнейшее масштабирование устройств, но и у нее есть свои пределы – это 7 нм рубеж. Поэтому Gate-all-Around является перспективной технологией и в будущем рассматривается как замена FinFET.