Программируемые логические интегральные схемы (ПЛИС): языки конфигурирования

16

16 Программируемые логические интегральные схемы (ПЛИС) занимают особое место в создании цифровых устройств. Они популярны, потому что на них реализуют аппаратную логику любой сложности без собственного ASIC. Однако для работы с ПЛИС требуется владение языками описания аппаратуры — VHDL и Verilog. Эти языки стали фундаментом индустрии FPGA, а их стандартизация позволила сформировать унифицированную экосистему средств САПР, библиотек и моделей.

В статье мы разберём различия между VHDL и Verilog и покажем, что освоить ПЛИС — проще, чем кажется.

![]() Время чтения: 12 минут

Время чтения: 12 минут

- Возможности

- Компиляция

- Типы данных

- Пакетное проектирование

- Самый простой в освоении

- Прямая и обратная аннотация

- Высокоуровневые конструкции VHDL

- Расширения языка

- Библиотеки

- Низкоуровневые конструкции

- Управление большими проектами

- Операторы

- Параметризуемые модели

- Процедуры и задачи

- Удобочитаемость

- Структурная репликация

- Тестовые программы

- Многословность VHDL

ПЛИС? Это очень просто!

Сегодня есть два отраслевых стандарта языков описания оборудования: VHDL и Verilog. Сложность проектирования микросхем ASIC и FPGA привела к увеличению числа специалистов, которые разрабатывают специальные инструменты и собственные библиотеки как на VHDL, так и Verilog.

Важно, чтобы проектировщики знали как VHDL, так и Verilog, а поставщики средств автоматизированного проектирования (САПР) предоставляли инструменты, в среде которых используются оба языка одновременно. К примеру, у проектировщика есть модель интерфейса шины PCI, написанная на VHDL, но он хочет использовать её в проекте с макросами, написанными на Verilog.

VHDL (англ. VHSIC (Very high speed integrated circuits) Hardware Description Language) — язык описания оборудования сверхбыстрых интегральных схем — стал стандартом IEEE 1076 в 1987 году. Он обновлён в 1993 году и известен сегодня как «стандарт IEEE 1076-1993».

Язык описания оборудования Verilog используется дольше, чем VHDL — с момента запуска в коммерческую эксплуатацию компанией Gateway в 1983 году. Компания Cadence приобрела Gateway в 1989 году и открыла Verilog для всех в 1990 году. Он стал стандартом IEEE 1364 в декабре 1995 года.

Возможности

При моделировании абстрактного оборудования возможности VHDL иногда могут быть реализованы только на Verilog с использованием PLI. Таким образом, выбор языка зависит не только от технических возможностей, но и от:

- предпочтений;

- доступности подходящей САПР;

- коммерческих, деловых и маркетинговых моментов.

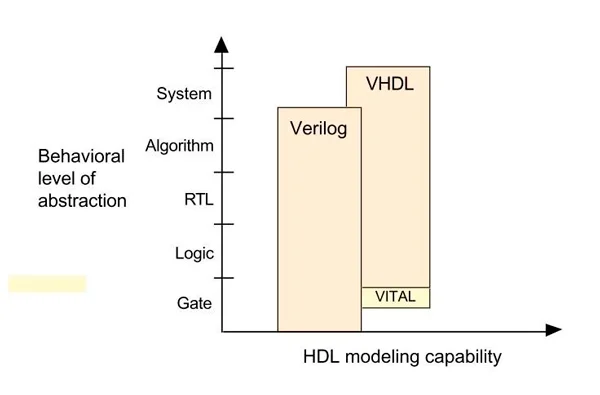

Области возможностей VHDL и Verilog охватывают несколько различный спектр на разных уровнях поведенческой абстракции.

Компиляция

VHDL. Несколько проектных единиц (пар «сущность/архитектура»), находящихся в одном системном файле, при необходимости компилируются отдельно. Однако практичнее хранение каждой проектной единицы в отдельном системном файле, и тогда отдельная компиляция не вызывает проблем.

Verilog. Язык Verilog основан на собственном режиме интерпретации кода. Компиляция — это средство ускорения моделирования, но она не меняет исходной природы языка. Поэтому необходимо соблюдать осторожность как с порядком компиляции кода, написанного в одном файле, так и с порядком компиляции нескольких файлов. Результаты моделирования поменяются с изменением порядка компиляции.

Типы данных

VHDL. Можно использовать множество языковых или пользовательских типов данных. Это может означать, что для преобразования объектов из одного типа в другой потребуются специальные функции преобразования. Выбирать используемые типы следует тщательно, особенно для перечислимых (абстрактных) типов данных. Это упростит написание моделей, сделает их более понятными для чтения и позволит избежать ненужных функций преобразования, которые могут загромождать код. VHDL предпочтительнее, поскольку позволяет использовать множество языковых или пользовательских типов данных.

Verilog. По сравнению с VHDL, типы данных Verilog очень просты, удобны в использовании и в значительной степени ориентированы скорее на моделирование аппаратной структуры, в отличие от абстрактного аппаратного моделирования. В отличие от VHDL, все типы данных, используемые в модели Verilog, определяются только языком Verilog, а не пользователем.

Существуют сетевые типы данных, например, wire, и регистровый тип данных, называемый reg. Модель с сигналом, тип которого — один из сетевых типов данных, имеет соответствующий электрический проводник в подразумеваемой моделируемой схеме. Объекты, то есть сигналы типа reg, сохраняют свои значения в течение дельта-циклов моделирования и не следует путать их с моделированием аппаратного регистра. Verilog предпочтительнее из-за простоты.

Пакетное проектирование

VHDL. Процедуры и функции могут быть помещены в пакет, чтобы быть доступными любому проектному блоку, который захочет их использовать.

Verilog. В Verilog нет концепции пакетов. Функции и процедуры, используемые в модели, должны быть определены в модуле. Чтобы сделать функции и процедуры общедоступными из различных операторов модуля, они должны быть помещены в отдельный системный файл и включены с помощью директивы компилятора include.

Самый простой в освоении

Если начинать с нулевого знания обоих языков, Verilog, пожалуй, самый простой для освоения и понимания. При этом предполагается, что язык директив компилятора Verilog для моделирования и язык PLI не учитываются. В противном случае их рассматривают как два дополнительных языка, требующих изучения.

VHDL кажется менее интуитивным поначалу по двум основным причинам. Во-первых, он типизирован, что делает его надёжным и мощным для опытных пользователей после длительного периода обучения. Во-вторых, есть много способов моделирования одной схемы, особенно с большими иерархическими структурами.

Прямая и обратная аннотация

Стандартный формат задержки (SDF) — ответвление Verilog. Это универсальный формат, используемый для определения временны́х задержек в схеме. Он обеспечивает двунаправленную связь между инструментами топологии кристалла и инструментами синтеза или моделирования, обеспечивая более точное представление временных задержек. Формат SDF теперь является самостоятельным отраслевым стандартом.

Высокоуровневые конструкции VHDL

В VHDL больше конструкций и функций для высокоуровневого моделирования, чем в Verilog. Абстрактные типы данных применимы вместе со следующими операторами:

- операторы package для повторного использования модели;

- операторы configuration для настройки структуры проекта;

- операторы generate для репликации структуры;

- универсальные операторы для универсальных моделей, характеризуемые индивидуально, к примеру, разрядностью.

Все эти операторы языка полезны в синтезируемых моделях Verilog. За исключением возможности параметризации моделей путём перегрузки констант параметров, в Verilog нет эквивалента высокоуровневым операторам моделирования VHDL.

Расширения языка

Использование расширений языка сделает модель нестандартной и, скорее всего, непереносимой для других инструментов проектирования. Однако иногда они необходимы:

VHDL. Имеет атрибут foreign, который позволяет моделировать архитектуры и подпрограммы на другом языке.

Verilog. Интерфейс языка программирования (PLI) — это интерфейсный механизм между моделями Verilog и программными инструментами Verilog. К примеру, разработчик или, что более вероятно, поставщик инструментов Verilog может указать пользовательские задачи или функции на языке программирования C, а затем вызвать их из исходного описания Verilog.

Использование таких задач или функций делает модель Verilog нестандартной и, следовательно, может быть непригодной для использования другими инструментами Verilog. Их использование не рекомендуется.

Библиотеки

VHDL. Библиотека — это хранилище скомпилированных сущностей, архитектур, пакетов и конфигураций. Полезно для управления несколькими проектами.

Verilog. В Verilog нет понятия библиотеки. Это связано с тем, что Verilog изначально был интерпретируемым языком.

Низкоуровневые конструкции

VHDL. В язык встроены простые логические операторы с двумя входами: NOT, AND, OR, NAND, NOR, XOR и XNOR. Любые временные задержки должны быть указаны отдельно с помощью предложения after. Для определения примитивов ячеек библиотек ASIC и FPGA должны использоваться отдельные конструкции, определённые в языке VITAL.

Verilog. Язык Verilog изначально разрабатывался с учётом моделирования на уровне вентилей, поэтому имеет очень хорошие конструкции для моделирования на этом уровне, а также для моделирования примитивов ячеек библиотек ASIC и FPGA. Примерами служат определяемые пользователем примитивы (UDP), таблицы истинности и блок спецификаций для задания временны́х задержек в модуле.

Управление большими проектами

VHDL. Операторы конфигурации, генерации, обобщения и упаковки помогают управлять большими структурами проектов.

Verilog. В Verilog нет операторов, помогающих управлять большими проектами.

Операторы

Большинство операторов одинаковы в обоих языках. В Verilog есть очень полезные унарные операторы редукции, которых нет в VHDL. Оператор цикла может использоваться в VHDL для выполнения той же операции, что и унарный оператор редукции Verilog. В VHDL есть оператор mod, которого нет в Verilog.

Параметризуемые модели

VHDL. Модель с заданной разрядностью может быть создана из обобщённой n-битной модели с помощью оператора generic. Обобщённая модель не будет синтезирована, пока не будет создана и не будет указано значение обобщения.

Verilog. Модель с заданной разрядностью может быть создана из обобщённой n-битной модели с использованием перегруженных значений параметров. Для обобщённой модели должно быть определено значение параметра по умолчанию. Это означает два момента. Если перегруженное значение не указано, синтез будет выполнен, но с использованием указанного значения параметра по умолчанию. Кроме того, для синтеза не нужно создавать модель с указанием перегруженного значения параметра.

Процедуры и задачи

VHDL допускает одновременные вызовы процедур. Verilog не допускает одновременных вызовов задач.

Удобочитаемость

Это скорее вопрос стиля кодирования и опыта, чем особенностей языка. VHDL — многословный язык, его корни берут начало в языке Ada. Verilog больше похож на язык C, поскольку его конструкции основаны примерно на 50% на C и на 50% на Ada. Поэтому программист, владеющий языком C, предпочитает Verilog. В случае VHDL, программист, владеющий и C, и Ada, может поначалу счесть сочетание конструкций запутанным. Какой язык HDL ни использовать, при написании или чтении синтезируемой HDL-модели важно учитывать особенности аппаратного обеспечения.

Структурная репликация

VHDL. Оператор generate копирует несколько экземпляров одного элемента проекта или его части и соответствующим образом их связывает.

Verilog. В Verilog нет эквивалента оператору generate.

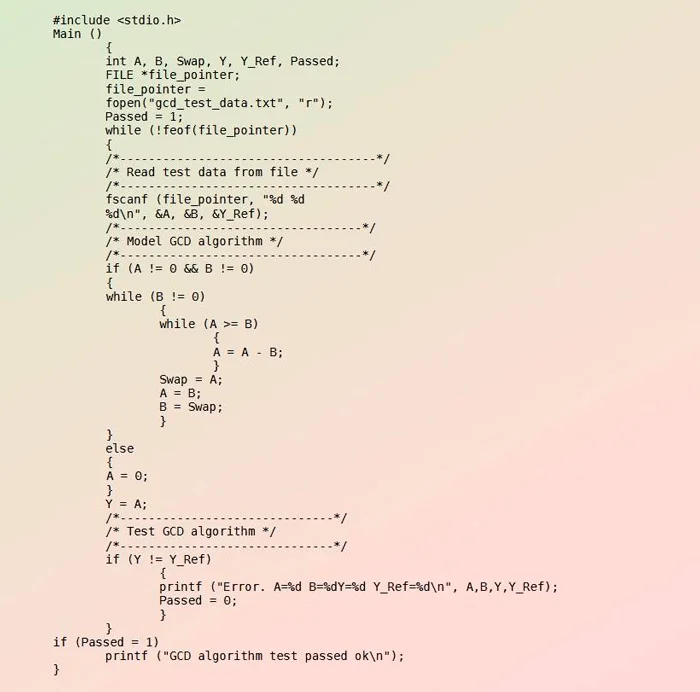

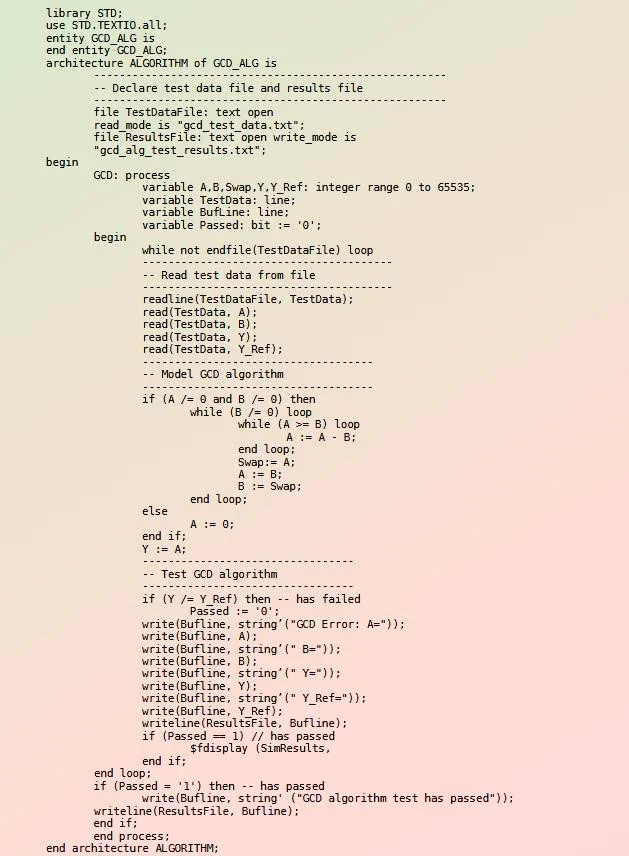

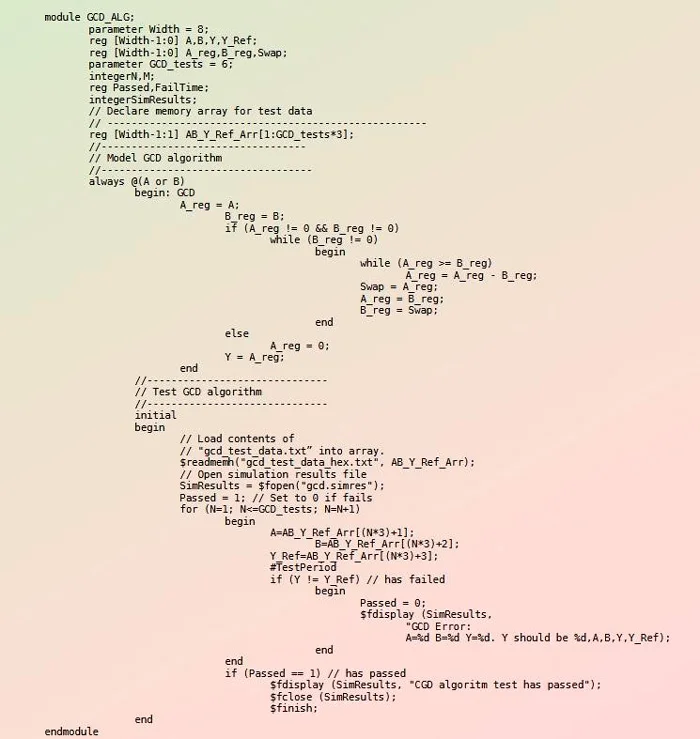

Тестовые программы

Разработчики обычно тратят около 50% своего времени на написание синтезируемых моделей, а остальные 50% — на написание тестовой программы для их проверки. Тестовые программы не ограничены синтезируемым подмножеством и поэтому используют весь потенциал языка. В VHDL есть общие и конфигурационные операторы, полезные в тестовых программах, которых нет в Verilog.

Многословность VHDL

Поскольку VHDL — типизированный язык, модели кодируются с точным соответствием и определением типов данных. Это как преимущество, так и недостаток. Однако это означает, что модели часто более многословны, а код часто длиннее, чем их эквивалент в Verilog.

В случае Verilog, сигналы, представляющие объекты разной разрядности, могут быть назначены друг другу. Сигнал, представляющий меньшее количество бит, автоматически дополняется сигналом с множеством бит, и не зависит от того, назначен ли он сигналу или нет. Неиспользуемые биты будут автоматически оптимизированы и удалены в процессе синтеза. Преимущество этого в том, что не нужно столь явное моделирование, как в VHDL, но это означает, что непреднамеренные ошибки моделирования не будут обнаружены анализатором.

Если сравнивать программируемые логические интегральные схемы (ПЛИС) с, к примеру, микроконтроллерами, то «налицо» будет повышенная аппаратная сложность ПЛИС, а также порог вхождения в их конфигурирование (программирование). Необходимость досконально разбираться во внутреннем устройстве конкретной ПЛИС, изучать узкоспециализированные VHDL и Verilog, приобретать оригинальные и порой дорогие программаторы — всё это отпугивает «ардуинщиков» от изучения этой поистине уникальной области электроники, находящейся в авангарде технологий.

А зря! Возможности нынешних, даже недорогих программируемых логических интегральных микросхем безграничны и перекрывают всё, что только способен придумать разработчик-любитель. Обилие литературы и материала в интернете поможет быстро освоить базу языков VHDL и Verilog, Суперайс готов поставить всё необходимое для разработки оборудование. Да и приобщение к области, по сути, профессиональной, многого стоит! Изучайте, пробуйте, и у вас всё получится!

Читайте также другие части цикла:

59

59

101

101

294

294