Программируемые логические интегральные схемы (ПЛИС): разновидности

29

29 Программируемые логические интегральные схемы (ПЛИС, PLD) прошли долгий путь от первых массивов И–ИЛИ до сложнейших FPGA, содержащих сотни тысяч логических элементов, высокоскоростные интерфейсы и встроенные процессорные ядра. Несмотря на значительную технологическую эволюцию, базовый принцип остался прежним: конфигурируемая логическая структура выполняет аппаратные функции, определяемые пользователем.

В статье рассмотрим развитие ПЛИС от PLA и PAL до GAL, CPLD и современных FPGA, а также разберём, какие идеи ранних устройств сохранились сейчас. Материал покажет, почему ПЛИС стали важнейшей платформой для создания цифровых систем и как этот термин почти полностью стал синонимом FPGA.

Предыдущую статью на тему программируемых логических интегральных схем (ПЛИС) вы можете прочитать здесь.

![]() Время чтения: 16 минут

Время чтения: 16 минут

ПЛИС? Это очень просто!

Эволюция ПЛИС — это пример того, как последовательное развитие относительно простой идеи приводит к появлению мощных устройств, способных заменить специализированные микросхемы, ускорить разработку и дать гибкость, недоступную инженерам. От первых PLA/PAL до современных FPGA прошли десятилетия, но принципы остались такими же: конфигурируемая логика, параллельность и высокая степень адаптивности.

PLA и PAL

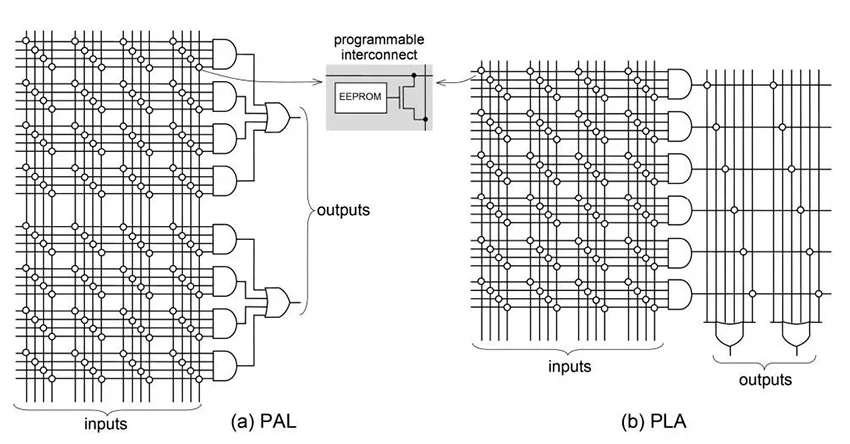

Программируемые логические вентильные матрицы PLA и PAL — это разновидности ранних ПЛИС. Разница между PLA и PAL в том, что PAL состоит из программируемого массива вентилей И и непрограммируемого массива вентилей ИЛИ. В PLA же оба массива вентилей (И и ИЛИ) программируемые.

Следовательно, более гибкие возможности программирования ПЛИС типа PLA позволяют реализовать сложные комбинаторные логические схемы. Но более сложная внутренняя структура ПЛИС типа PLA, изобилующая длинными линиями, имеющими немалое сопротивление и паразитную ёмкость приводит к заметному снижению скорости её работы.

Этот недостаток и высокая стоимость стали причиной нынешней непопулярности ПЛИС типа PLA, хотя PAL до сих пор широко используются (но не разрабатываются, как собственно и GAL, уступив место более совершенным разновидностям CPLD и FPGA).

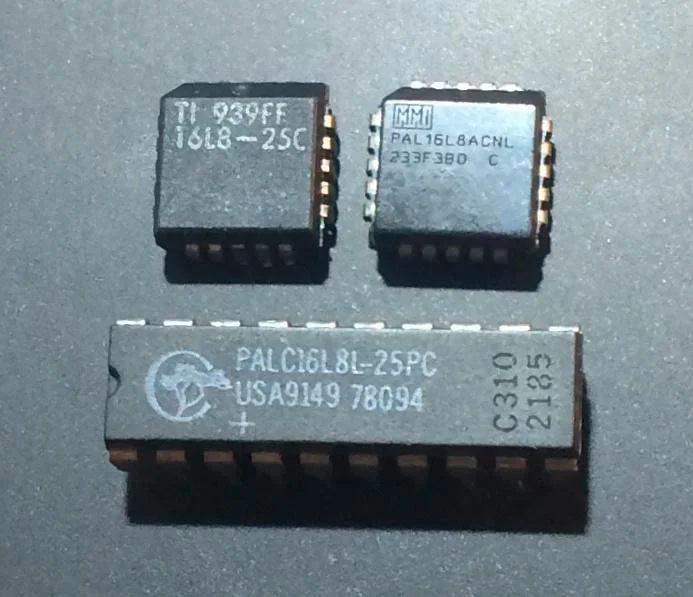

GAL

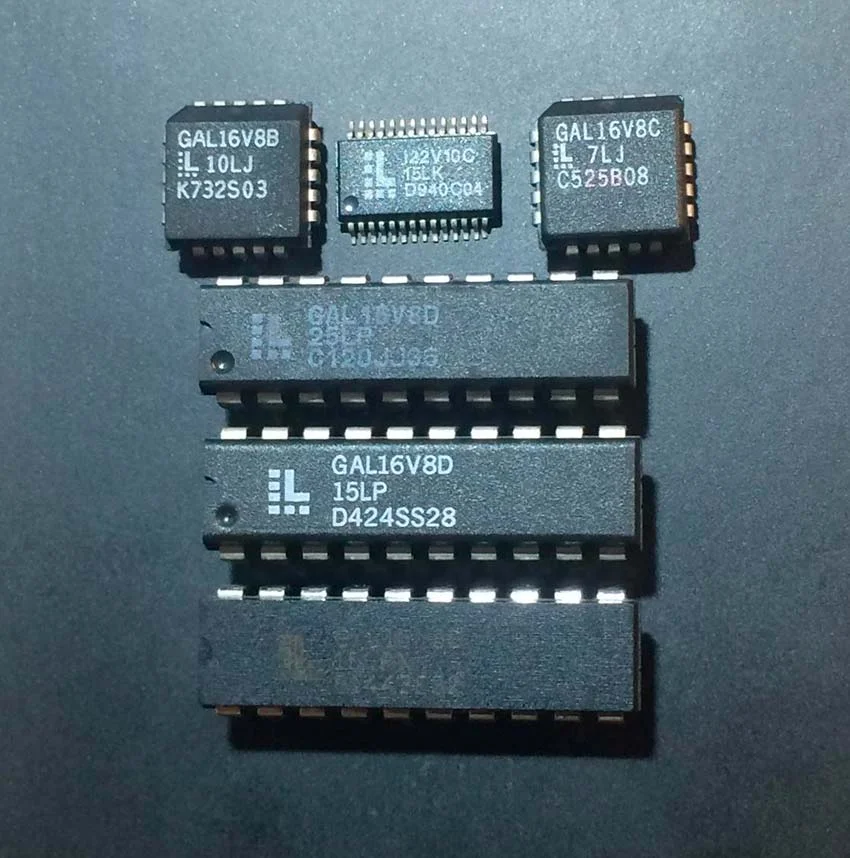

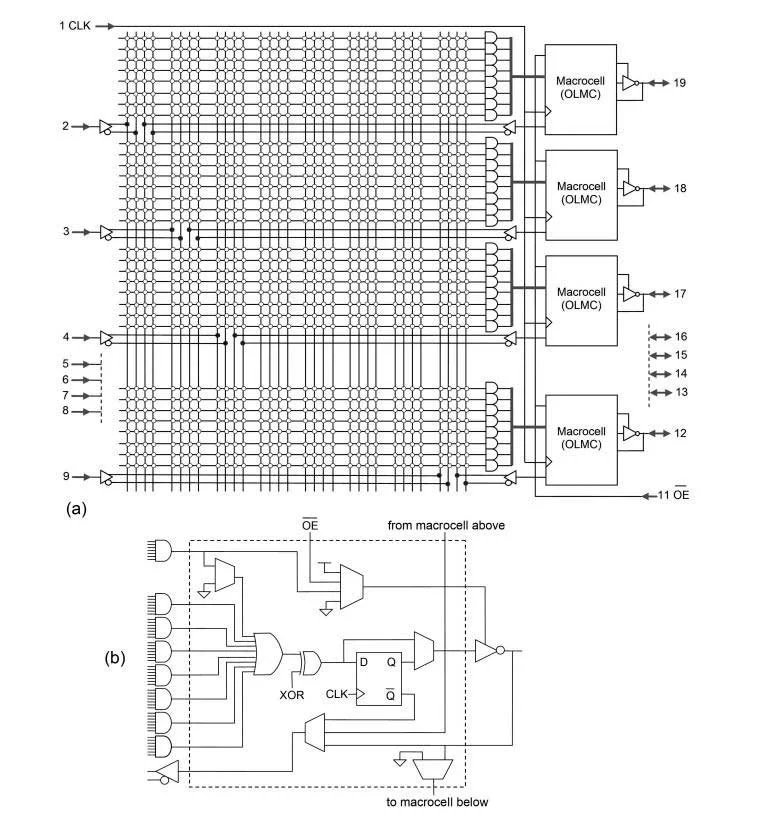

Технология GAL в значительной мере популяризировала и дала начало массовому внедрению ПЛИС. GAL базируется на технологии PAL с отдельной макроячейкой на каждом выходе. Успешным устройством в этом подходе стала ПЛИС GAL16V8 (изображённая на рисунке выше) с шестнадцатью входами и восемью выходами в двадцативыводном корпусе (восемь выводов двунаправленные).

Видны улучшения по сравнению с PAL:

- возможность выбора регистрового или нерегистрового выхода (благодаря триггеру);

- выбор инвертированного или неинвертированного выхода (благодаря схеме XOR);

- выход с тремя состояниями (логический ноль, логическая единица, высокоимпедансное или, по-другому, Z-состояние);

- выходной сигнал отправляется обратно в программируемую матрицу (ему не нужно выходить из кристалла и возвращаться при реализации сложных коммутационных схем, что повышает скорость работы ПЛИС и снижает расход конфигурационной памяти);

- прямое соединение между соседними ячейками (с аналогичными преимуществами).

Хотя GAL сегодня представляет лишь исторический интерес, понимание этого типа ПЛИС крайне важно. Поскольку, как будет показано далее, и CPLD, и FPGA тесно связаны с GAL.

CPLD

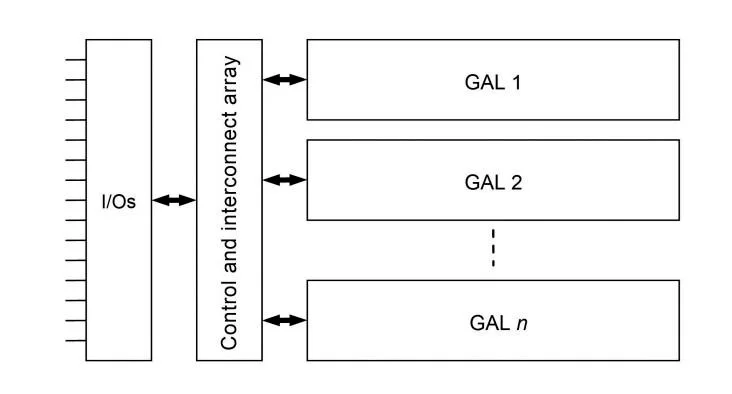

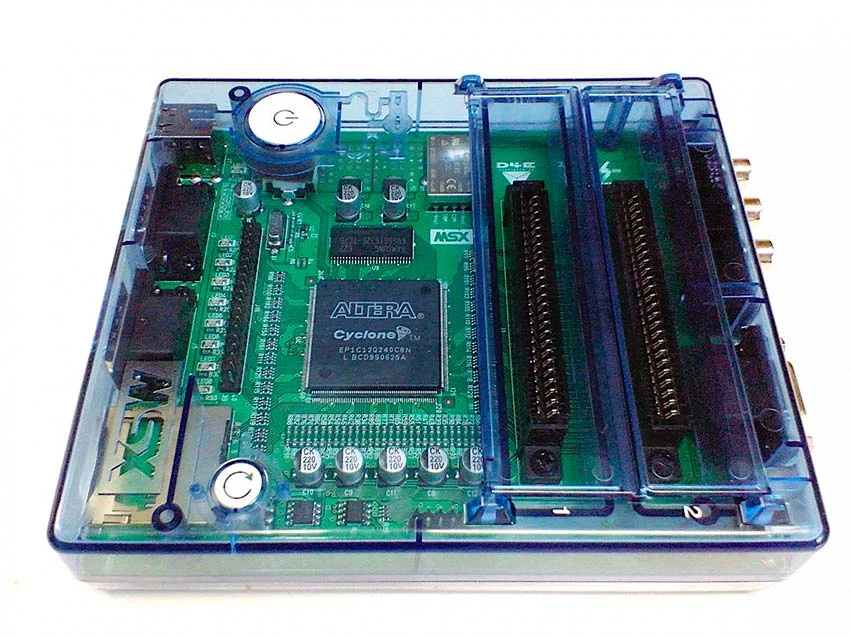

Технология ПЛИС типа CPLD была представлена компанией Altera с её первым устройством — EP300, увидевшим свет в 1984 году. Если длинную историю сделать краткой, то CPLD — это относительно небольшой массив из блоков типа GAL среднего размера (рисунок выше), по-прежнему с энергонезависимой конфигурационной памятью, но с некоторыми дополнительными функциями по сравнению с GAL. Улучшены внутренние межсоединения, более сложная сеть синхронизации и большие возможности ввода-вывода.

Примером «классического» семейства CPLD (следовательно, использующего общую архитектуру как на рисунке выше) является старая серия MAX3000 от Altera, построенная на 2, 4, 8, 16 или 32 структурами типа GAL. Каждая имеет шестнадцать макроячеек (Altera называла такие структуры «блоками логической матрицы», Logic Array Block, LAB). Следовательно, общее количество макроячеек (и, следовательно, триггеров) в этом семействе от 32 до 512. Другим примером «настоящего» семейства CPLD, на этот раз от Xilinx, является старая (но до сих пор применяемая в разработке новых устройств) серия XC9500, построенная на 2, 4, 6, 8, 12 или 16 GAL-подобных структурам, где у каждой восемнадцать макроячеек.

Основной недостаток PAL-устройств (все рассмотренные ПЛИС, включая CPLD) — они плохо масштабируются с развитием технологий. Обратите внимание на рисунок (в разделе PLA и PAL), что количество программируемых точек учетверяется при удвоении количества входов (и размера слоя И). Следовательно, сильно усложняется внутренняя коммутационная структура ПЛИС (к примеру, образующиеся длинные, сильно нагруженные линии влияют на скорость работы и энергопотребление). Имеющиеся недостатки практически поставили крест на развитии CPLD. Компании либо прекращают их производство, либо используют вместо них «упрощённые» ПЛИС с энергонезависимой памятью для конфигурационных переключателей (SRAM заменяется flash-памятью). Так что с точки зрения пользователя всё выглядит так же.

Примерами таких «псевдо-CPLD» стали семейства Altera MAX II, MAX V и MAX 10, которые Intel теперь (и это правильно) называет FPGA вместо CPLD. Вкратце, это простые и дешёвые ПЛИС, но с энергонезависимой конфигурационной памятью (и, конечно же, программируемая И/ИЛИ-матрица заменена таблицей преобразования LUT).

FPGA

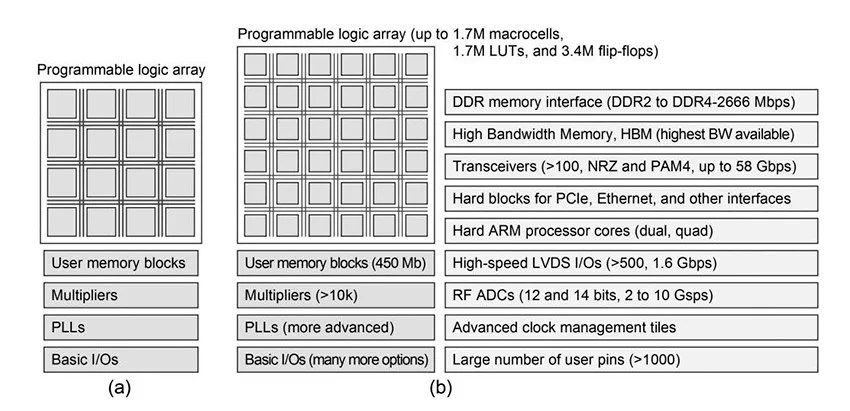

В отличие от CPLD с большими И-ИЛИ массивами (и их длинными, медленными линиями), в матричной архитектуре FPGA они были заменены компактными таблицами преобразования (LUT). Также использование SRAM-памяти вместо flash-памяти для конфигурирования позволяют хорошо масштабироваться вместе с развитием технологий, по полной используя преимущества новейших техпроцессов изготовления микроэлектронных приборов. N-входовая таблица преобразования (LUT) может реализовать любую булевую функцию с N-переменными, что в общем случае неверно для N-входовых И-ИЛИ массивов SPLD и CPLD.

Рисунок выше иллюстрирует, как FPGA выглядели на заре развития (a). Их ядро, программируемая логическая матрица, представляла собой относительно скромную матрицу небольших кластеров макроячеек, подобных глобальным спискам адресов (как у GAL), но с таблицами преобразования (LUT) вместо массивов И-ИЛИ (как у PLA и PAL) для вычисления логических функций и со статической оперативной памятью (SRAM) вместо flash-памяти для конфигурирования.

Дополнительные функции — несколько пользовательских блоков SRAM, аппаратные умножители (для реализации цифровой обработки сигналов, Digital Signal Processing, DSP), незаменимые схемы фазовой автоматической подстройки частоты (ФАПЧ, для управления тактовой частотой) и набор базовых стандартов ввода-вывода (3.3 В LVCMOS, LVDS и т. д.).

Текущее положение дел с FPGA показано на рисунке выше (b). Программируемая логическая матрица значительно больше, как и её первоначальные функции (перечисленные в блоке логической матрицы). Но, что ещё важнее, теперь доступен ряд весьма сложных устройств (перечислены справа на рисунке), включая высокоскоростную память (HBM) с самой высокой пропускной способностью в отрасли, самые быстрые приёмопередатчики на рынке (например, для интернет-инфраструктуры), аппаратно поддерживаемые протоколы для нескольких стандартов связи (PCI Express, 10G XAUI, 100G Ethernet и т. д.), аппаратные ядра процессоров ARM (для вычислений общего назначения) и т. д.

Подводя итог, скажем, что FPGA теперь — сложная «экосистема», созданная на новейших технологиях под разные приложения.

Вот особенности и преимущества FPGA:

- Они позволяют создавать решения, которые были бы технически неполноценными или невыгодными при других подходах, особенно на базе устройств из списка на рисунке выше.

- Решения адаптируются точно под целевое приложение. Это оптимизирует системы, например, ускорению за счёт параллелизма и снижению энергопотребления за счёт правильной архитектуры схемы и управления тактовой частотой. Также подходит для сложных математических вычислений.

- Проекты разрабатываются гораздо быстрее и не связаны с рисками и единовременными затратами на проектирование (Non-Recurring Engineering, NRE), характерными для решений на базе ASIC.

- В отличие от ASIC, проекты обычно легко модифицируются. Это полезно для соответствия новым стандартам или другой специфики.

- В отличие от CPLD, они легко извлекают «выгоду» из прогресса в технологии производства устройств: способны идти «в ногу со временем».

И, что удивительно, их легко программировать! Языки VHDL и Verilog, а также современные компиляторы и симуляторы делают эту задачу очень доступной. Моделирование также значительно проще, чем в ASIC, поскольку аппаратное обеспечение уже сконфигурировано производителем.

Архитектура современных FPGA

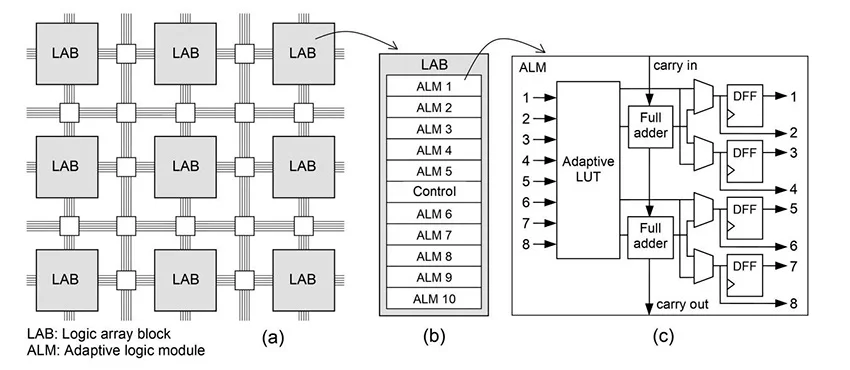

На рисунке представлен обобщённый архитектурный подход Intel, используемый, к примеру, в его топовом семействе Stratix 10. Архитектура состоит из большой матрицы блоков LAB, показанной на (a). Содержимое каждого LAB показано на (b), состоящем из 10 блоков адаптивных логических модулей (Adaptive Logic Module, ALM).

Наконец, содержимое каждого ALM изображено на (c), где можно увидеть LUT (с восемью входами, делящимися на два или более меньших LUT), за которыми следуют мультиплексоры и триггеры, которые позволяют регистрировать или не регистрировать выходы, а также позволяют осуществлять прямое соединение между соседними блоками. Это полезно, например, при построении быстрых арифметических схем. Обратите внимание на общее сходство между этой схемой и макроячейкой GAL.

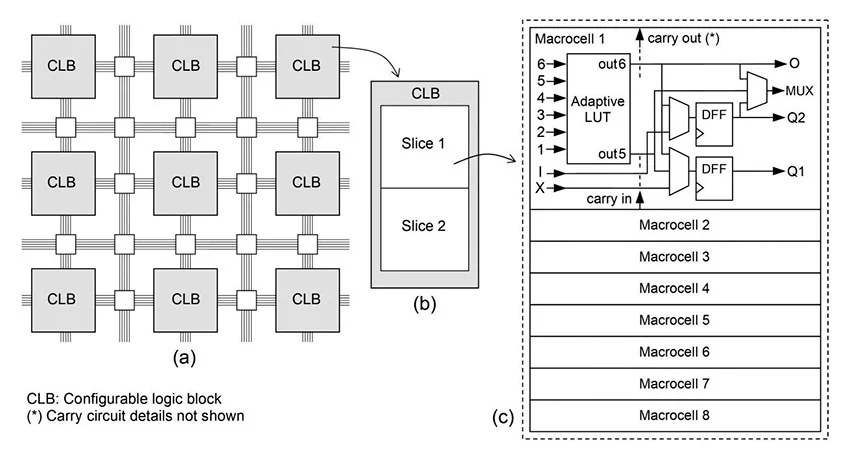

На рисунке ниже представлен действующий архитектурный подход Xilinx, используемый, к примеру, в её топовом семействе Virtex UltraScale+.

Обратите внимание, что общая архитектура похожа, только с другим названием логического блока, который здесь называется конфигурируемым логическим блоком (Configurable Logic Block, CLB). Содержимое каждого CLB, состоящего из двух блоков Slice, показано на рисунке (b). Наконец, содержимое каждого блока Slice показано на рисунке (c), где в каждой из восьми схем, составляющих один блок Slice, снова представлены таблица преобразования (LUT), мультиплексоры и триггеры. Для простоты эти схемы также будут по отдельности (и неформально) называться «макроячейками».

Таким образом, каждый LAB содержит десять таблиц соответствия (LUT) и сорок блоков DFF, в то время как каждый блок CLB содержит шестнадцать таблиц соответствия (LUT) и тридцать два блока DFF. Это стандартные ячейки, поэтому различия между FPGA того же семейства в отношении логической матрицы FPGA заключаются лишь в количестве LAB или CLB в (большой) матрице.

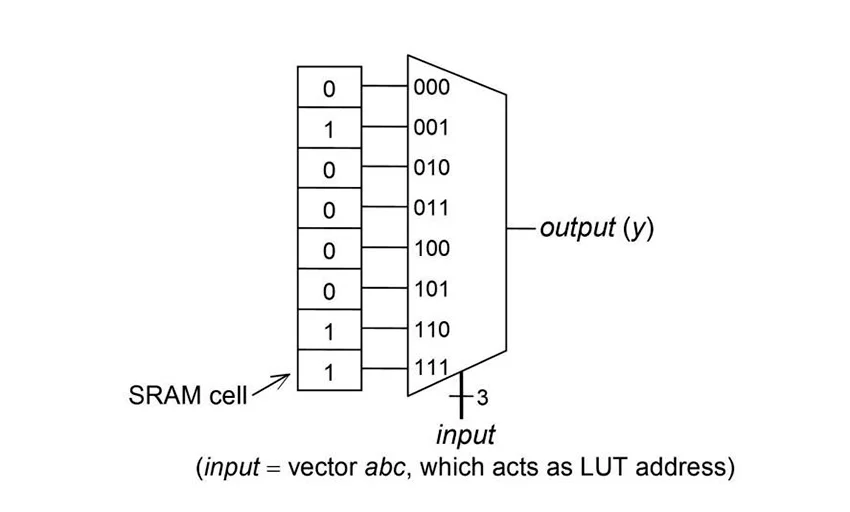

Конструкция LUT показана на рисунке ниже (для N = 3 входов). Она состоит из статического ОЗУ (SRAM) и мультиплексора. Поскольку память содержит 2N адресов, с её помощью может быть реализована любая N-битная функция. Например, обратите внимание, что SOP, реализованный на рисунке ниже для заданного содержимого SRAM, выглядит следующим образом: y = a * b + a′ * b′ * c, как и в примере в начале статьи.

Семейства современных FPGA

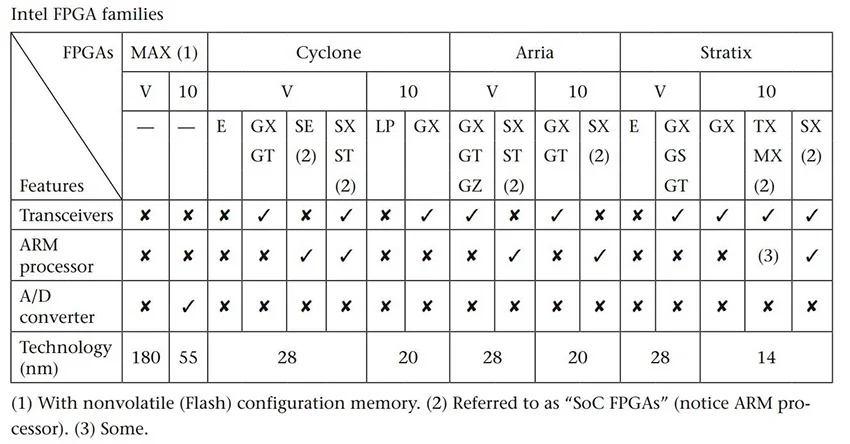

В таблице ниже показаны все текущие семейства FPGA Intel, а именно (от низшего к высшему) MAX, Cyclone, Arria и Stratix. Там же показаны последние два поколения (V и 10) для каждого семейства и соответствующие технологии. Обратите внимание, что устройства MAX используют старые технологии (180 нм и 55 нм), в то время как Cyclone и Arria используют относительно новые технологии (28 нм и 20 нм), а Stratix 10 использует ещё более тонкий технологический процесс (14 нм).

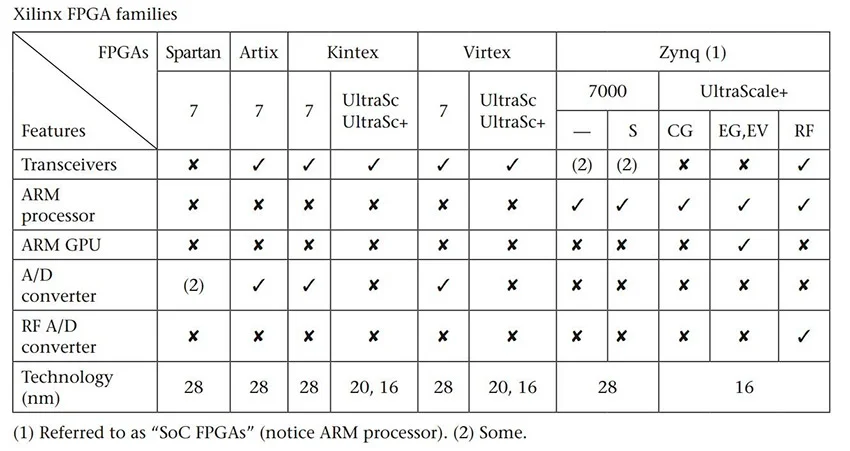

К примеру, когда микропроцессор (всегда одно или несколько ядер ARM) встроен в структуру FPGA, такая серия называется «система на кристалле» или SoC (System-on-Chip), поскольку на её основе можно легко построить довольно сложные системы. В таблице ниже представлены все текущие семейства Xilinx, к которым (от низшего к высшему) относятся Spartan, Artix, Kintex и Virtex. Там же представлены устройства семейства Zynq, которые являются SoC из-за наличия аппаратных микропроцессоров (ARM). Последние три поколения Xilinx — это 7, UltraScale и UltraScale+, в которых используются технологические процессы 28 нм, 20 нм и 16 нм соответственно.

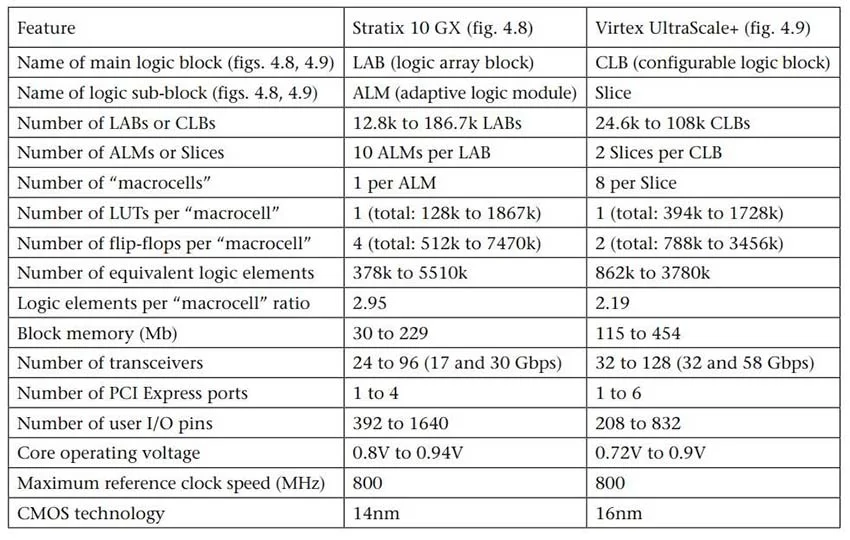

В таблице показаны важные характеристики двух топовых FPGA схожих категорий: Stratix 10 GX от Intel, а второе Virtex UltraScale+ от Xilinx.

Обратите внимание, что общее количество таблиц преобразования (LUT), триггеров и эквивалентных логических элементов хорошо перекрывается. Ещё учитывайте сходство других характеристик, таких как рабочее напряжение ядра и максимальная опорная тактовая частота.

Возможности и стоимость современных FPGA

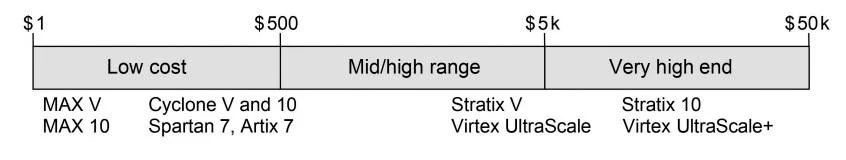

Стоит кратко рассказать цене нынешних ПЛИС типа FPGA, которая составляет от одного до десятков тысяч долларов.

Современные Cyclone, Spartan и Artix обычно попадают в первый низкобюджетный диапазон, а Stratix и Virtex — в верхнюю часть второго среднебюджетного и в третий высокобюджетный диапазоны. Важно, однако, подчеркнуть, что устройства в недорогом диапазоне бывают мощными.

К примеру, начальная версия Cyclone 10 GX, содержащая 31 тысячу ALM (85 тысяч эквивалентных логических элементов), шесть высокоскоростных (12.5 Гбит/с) приёмопередатчиков, 6 мегабайт пользовательской оперативной памяти и множество других функций, стоит около 100 долларов. Spartan 7 с эквивалентным количеством логических ячеек 6 тысяч продают менее чем за 12 долларов, а MAX 10 — менее чем за 5 долларов.

Индустрия FPGA также предлагает немало плат разработки и программаторов, некоторые по специальным сниженным ценам для академического использования. Но всё же цена комплектов для профессиональных разработчиков чрезвычайно высока.

Современные FPGA — это уже не просто логические матрицы, а полноценные платформы с процессорами, высокоскоростными интерфейсами, гигабайтами встроенной памяти и потенциалом для создания систем разной сложности. При этом порог вхождения остаётся доступным: инструменты, языки описания аппаратуры и недорогие устройства каждому дают возможность познакомиться с ПЛИС — и убедиться, что это просто.

83

83

285

285

250

250