Тестирование печатных плат на производстве: методы и технологии. Часть 2

1.4K

1.4K Как было сказано в первой части статьи, выпуск 100%-качественной электронной продукции невозможен, но доступен выходной контроль печатных плат (ПП) после всех технологических операций. Он помогает в отбраковке неисправных плат, воспрепятствует комплектованию приборов неисправными. В общем, снижает выпуск бракованной продукции, недопустимый для солидных компаний. Ведь это грозит серьёзными экономическими и репутационными рисками.

Получается, что выходной контроль ПП обязан выполняться на производстве после завершения технологического цикла. Быть непременным заключительным этапом создания продукта.

В этой части я знакомлю читателя с основами тестирования печатных плат, а именно: с обоснованием необходимости и его методологией.

Первую часть вы можете прочитать здесь.

![]() Время чтения: 17 минут

Время чтения: 17 минут

- Методы и технологии тестирования

- Ручная визуальная инспекция (Manual Visual Inspection, MVI)

- Автоматическая оптическая инспекция (Automatic Optical Inspection, AOI)

- Автоматическая рентгенографическая инспекция (Automatic X-Ray Inspection, AXI)

- Внутрисхемное тестирование (In-Circuit Testing, ICT)

- Периферийное сканирование (Boundary-Scan Testing)

- Функциональное тестирование (Functional Testing, FT)

Методы и технологии тестирования

Ручная визуальная инспекция (Manual Visual Inspection, MVI)

Она основана на визуальном сравнении готовой платы с её эталонным изображением. Инспекция определяет, выглядит ли ПП так, как её эталон. Но не даёт определить, работает ли плата правильно, как того требуется.

У визуальной инспекции есть преимущества перед другими методами проверок. Вот главные:

- Ограничивает производство дефектных изделий на более ранней стадии производственного процесса.

- Помогает избежать траты ресурсов на выпуск заведомо дефектных изделий.

Например, MVI плат после нанесения пасты помогает исправить недостаток до того, как ПП поместят в паяльную печь, одновременно исключить её неправильное нанесение последующие заготовки. Дефекты, обнаруживаемые осмотром, определить электрическими испытаниями сложнее и дороже.

Многие дефекты, с лёгкостью обнаруживаемые визуально, но с трудом — электроиспытаниями на постоянном токе. Например, «мышиные укусы» и «шпоры». Эти изъяны требуют радиочастотных электрических испытаний с применением высокочастотных сигналов. Но такой вид тестирования относительно сложный и затратный.

Manual Visual Inspection обнаруживает дефекты, которые приводят к отказу только при эксплуатации: это связано с простотой обнаружения конкретных недостатков, влияющих на надёжность. Например, недостаточное количество припоя.

MVI напрямую зависим от квалификации персонала, вооружённого хорошим освещением и увеличительными стёклами. Инспекторы способны распознать дефект на ранних этапах выпуска печатной платы. Но этот метод, как правило, эффективен только с простыми платами. Однако контроль многослойных ПП недостаточно эффективен из-за крайне небольших размеров элементов, наличия внутренних соединений и слоёв, скрытых от глаз инспекторов паяных соединений микросхем в корпусах BGA и т. д.

По сравнению с электрическим тестированием MVI не требует физического контакта с инспектируемым объектом. Она:

- Обнаруживает недостаточное качество пайки и, следовательно, выявляет проблемы с надёжностью.

- Помогает быстро действовать при исправлении дефектов предыдущих этапов изготовления.

Однако использование этого подхода частично или полностью прекращено из-за недостатков, которые первоочерёдно возникли из-за появления чрезвычайно плотной и миниатюрной электроники:

- Функциональная работоспособность платы при визуальном контроле в принципе не определяется.

- Подход невозможен для многослойных плат и HDI-плат.

- Не обнаруживает дефекты, которые расположены под компонентами: микросхемы в корпусах BGA, внутренние скрытые слои.

- Осмотр сложных плат длится очень долго, а значит, дорого.

При сложной конструкции ПП, хотя это решение бывает достаточным для проверки всех возможных дефектов, обнаруживаемых визуально, оно затратно из-за длительности инспекции одной сложной платы. Есть риск, что это приведёт к большим финансовым потерям и снижению общей производительности предприятия.

Автоматическая оптическая инспекция (Automatic Optical Inspection, AOI)

Она была разработана для автоматизации ручного визуального контроля и включает использование методов обработки изображений и алгоритмов сравнения. Контроль здесь референтный: референтное (эталонное) изображение уже хранится в памяти вычислительного блока и сравнивается со снимком, сделанным камерой оптического контроля. AOI имеет преимущества:

- Нет физического контакта платы и тестового оборудования.

- Возможность обнаружения дефектной маркировки или мельчайших косметических недостатков.

- Получил более высокую скорость в сравнении с MVI.

Однако Automatic Optical Inspection страдает от следующих недостатков:

- Функциональную работоспособность платы определить не получится.

- Невозможно выявить дефекты, которые расположены под компонентами, например, микросхемами в корпусах BGA, и скрытые во внутренних слоях.

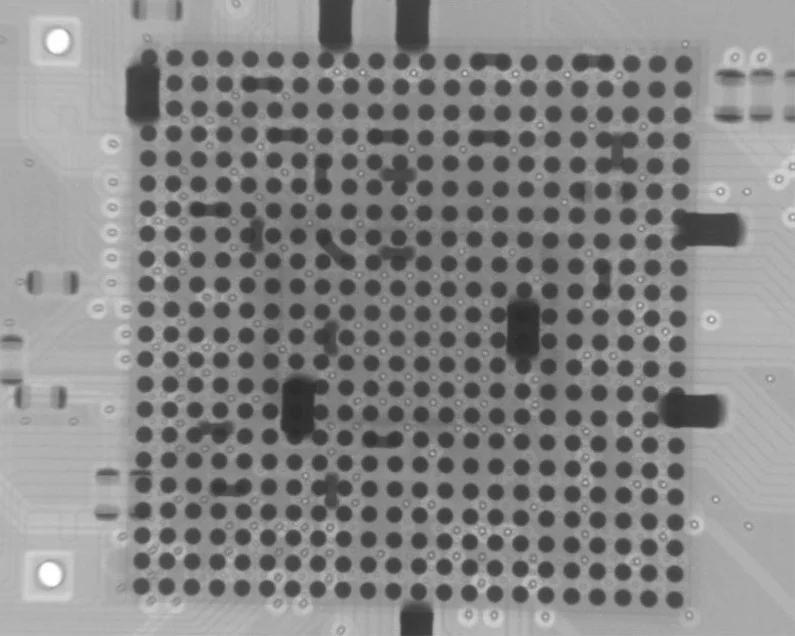

Автоматическая рентгенографическая инспекция (Automatic X-Ray Inspection, AXI)

Высокая миниатюризация электронных приборов требует компонентов с очень большим количеством выводов и их крайне малым шагом. Корпус BGA решил эту проблему: он позволяет размещать до нескольких тысяч выводов на микросхеме площадью всего в несколько квадратных сантиметров. Поскольку все выводы BGA находятся под корпусом, после оплавления визуально уже невозможно определить, дали ли шарики припоя требуемые соединения с контактными площадками.

Уже рассмотренные способы не способны обнаружить скрытые дефекты. Более того, даже внутрисхемное тестирование (In-Circiut Testing, ICT, рассмотрим его далее) не может в полноте протестировать платы с BGA-микросхемами. Для выхода из этой ситуации существует метод AXI. Он используется сразу после пайки для выявления дефектов под корпусами, под которыми скрыты паяные соединения, таких как BGA и CSP (Chip-Scale Package). Automatic X-Ray Inspection имеет ещё одно преимущество перед ICT: помогает проанализировать качество пайки и, таким образом, настроить процессы нанесения паяльной пасты и оплавления, через изучение полостей внутри паяных соединений и/или недостаточно расплавленных шариков припоя и/или избыточных или закороченных выводов из-за неверного количества пасты. Всё это даёт долгосрочную надёжность продукта. Преимущества AXI-метода обобщим так:

- Обнаружение коротких замыканий и мостов под корпусами компонентов, таких как BGA.

- Обнаружение пустот, других дефектов пайки для достижения долгосрочной надёжности конечного продукта.

- Корректировка и настройки нанесения паяльной пасты и оплавления, через анализ рентгенограмм.

К сожалению, текущая AXI-технология всё ещё нуждается в улучшении из-за следующих недостатков:

- Нелегко обнаружить обрывы между выводами и контактными площадками под BGA корпусами.

- Высокая стоимость рентгенографического оборудования.

- Низкая производительность.

Однако использование этой методики незаменимо при тестировании ПП с корпусами типа BGA, особенно когда платы создают для ответственных задач.

Внутрисхемное тестирование (In-Circuit Testing, ICT)

Оно предназначено для функционального тестирования платы с помощью серии контактных электрических измерений. ICT также известен как тестирование методом «белого ящика», в котором параметры проводимости, сопротивлении, ёмкости, импеданса и другие сравниваются с известными параметрами, заранее измеренными у эталонного устройства.

Тесты также проводят и с использованием тестовых площадок, размещённых разработчиком ПП так, чтобы измерить все необходимые электрические параметры всей схемы. Полное соответствие измеренных параметров с эталонными с высочайшей долей вероятности определяет полную функциональную исправность конечного устройства.

ICT имеет несколько преимуществ перед ранее обсуждавшимися визуальными и оптическими решениями:

- Возможность обнаружения неисправных или не соответствующих допускам компонентов.

- При наличии тестовых площадок метод способен обнаруживать скрытые и внутренние обрывы, короткие замыкания.

Однако ICT выполнимо только с зондированием (то есть прямым электрическим подключением), в которой есть только две альтернативы: либо дорогая, но быстрая система «стол с гвоздями» (Bed-of-nails system), либо автоматизированная, но медленная система с летающими зондами (Flying probe system). К сожалению, обе не идеальны, поэтому не всегда в полноте используются:

- Плотный монтаж не даёт дополнительного физического пространства для тестовых площадок.

- Внутренние дорожки платы в любом случае остаются недоступны.

- Прямой доступ к выводам компонентов в корпусах BGA и CSP невозможен.

- Зонды не применимы для тестирования высокочастотных устройств, так как будут выполнять роль приёмопередающих антенн, то есть нарушат работу схемы.

- Зондирование может быть фатальным для хрупких плат, особенно керамических, трудно применимо для гибких ПП.

Чуть подробнее рассмотрим две технологии внутрисхемного тестирования ICT, используемые сегодня. Выбор технологии обусловлен необходимой скоростью тестирования и величиной серийности выпуска продукции.

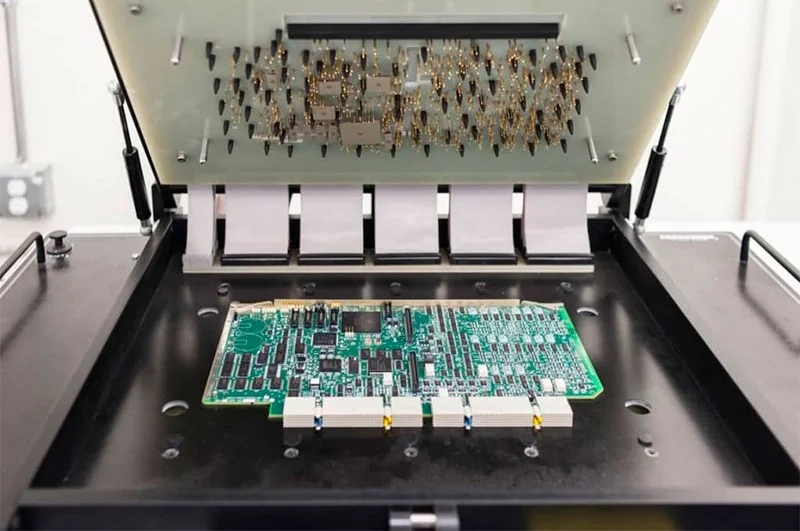

«Стол с гвоздями» (Bed-of-nails system)

Он специально создаётся для тестирования платы после одного конкретного этапа производства. То есть, это не решение «на все случаи жизни». Bed-of-nails позволяет тестировать по любым тестовым паттернам, заранее созданным и внесённым в конструкцию тестового стенда. Технология обладает высокой скоростью измерения, поскольку все тестовые зонды подключаются к тестируемой плате одновременно.

BON дорог в проектировании и изготовлении, поэтому «стол с гвоздями» подходит только для крупносерийного производства. Чтобы оправдать проектирование с изготовлением оснастки, нужны расходы, незначительные по сравнению с прибылью.

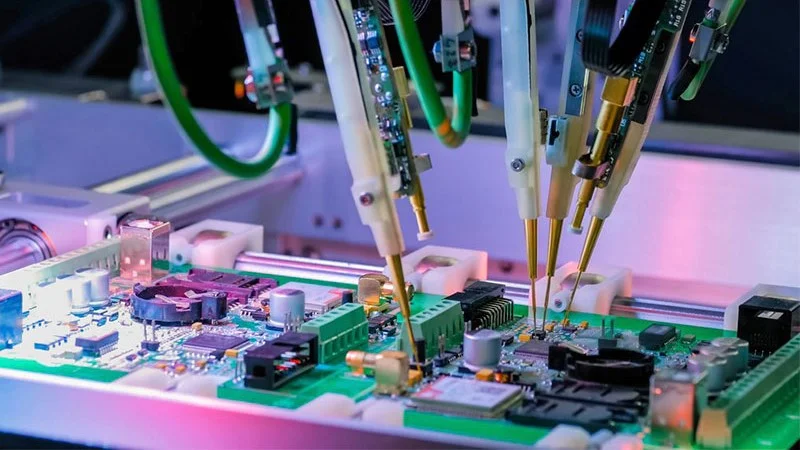

Летающие зонды (Flying probe system)

В отличие от «стола с гвоздями» эта система очень гибкая в плане универсальности. Хорошо подходит для измерения компонентов даже с очень малым шагом выводов. Автоматическая машина перемещает зонды от одних тестовых точек или выводов к другим по специально составленной карте замера.

Необходимость механического перемещения зондов между тестовыми точками приводит к низкой производительности, что стало фундаментальным недостатком такой технологии. Обычно производительность составляет от 5 до 10 контрольных точек в секунду (Test Point per second, TP/s). Использование системы летающих зондов оправдано только для мелкосерийного производства.

При рассмотрении FPS в качестве тестировочной технологии нужно учитывать несколько вопросов. Для эффективного и неразрушающего тестирования желательно измерять только с применением тестовых контрольных точек, а не выводов компонентов, которые в случае их сверхминиатюризации повреждаются машиной.

Также нужно тщательно составить карту замера для оптимизации времени перемещения зондов. Также этому способствует отсутствие высоких компонентов на плате для уменьшения расстояния подъёма зондов при перемещении.

Периферийное сканирование (Boundary-Scan Testing)

Это метод, разработанный специально для решения проблемы ограничения физического доступа к выводам компонентов. В области современных промышленных стандартов он известен как стандарт IEEE 1149.1.

Цифровые микросхемы, отвечающие стандарту, имеют специальный интерфейс связи, позволяющий с помощью внешнего измерительного оборудования подключиться к ним, чтобы выполнять необходимый комплекс тестирования. Помимо, собственно проверки их работоспособности, можно протестировать компоненты, напрямую взаимодействующих с ними. Обычно для достижения 100% покрытия всего спектра возможных неисправностей потребуются дополнительные тесты, например, зондирование. Из-за разнообразия используемых компонентов на ПП, ограниченного физического доступа стандарт IEEE 1149.1 становится недостаточным, и, таким образом, соединения со следующими компонентами остаются непроверенными:

- Пассивные компоненты.

- Цифровые микросхемы, не поддерживающие стандарт IEEE 1149.1.

- Микросхемы, работающие со смешанными сигналами: ЦАП, АЦП и другие (смотри статью «ТОП-10 типовых узлов в схемотехнике цифровых устройств»).

- Разъёмы.

Чтобы преодолеть проблемы ограниченных возможностей аналоговых измерений и тестирования пассивных компонентов, стандарт IEEE 1149.1 был расширен до IEEE 1149.4. Но IEEE 1149.4 не получил широкого коммерческого распространения. Среди причин: высокие затраты на его реализацию, низкая полоса пропускания частоты измерения, которая составляет приблизительно 1 мегагерц, более высокая погрешность измерения.

Стандарт IEEE 1149.1 не подходит для тестирования низковольтных дифференциальных линий связи (LVDS), распространённых в различной технике. Например, для подключения матриц дисплеев в компьютерных мониторах, ноутбуках или телевизорах. Чтобы решить эту проблему, был разработан IEEE 1149.6 для поддержки тестирования LVDS.

С точки зрения исследований стандарты периферийного сканирования сегодня достигли существенного прогресса в покрытии большинства возможных тестовых случаев. Однако тестирование открытых («висящих в воздухе») соединений было невозможно до появления стандарта IEEE 1149.8.1, который определяет тестирования именно открытых разъёмов.

Главное преимущество BST — возможность обнаружения обрывов, коротких замыканий под корпусами: например, BGA.

С другой стороны, с практической точки зрения, метод страдает от следующих недостатков:

- Ограничен в основном цифровыми устройствами.

- Минимум одна из микросхем должна быть совместима со стандартом IEEE 1149.

- Тестирование узлов без поддержки периферийного сканирования требует дополнительных усилий.

- Широко распространённые микросхемы памяти обычно не поддерживают периферийное сканирование.

- Метод не позволяет определить качество пайки и дефектов проводников.

Функциональное тестирование (Functional Testing, FT)

В отличие от внутрисхемного тестирования, FT проверяет не все возможные электрические соединения и параметры компонентов, а лишь определяет функциональную исправность устройства. Другими словами, оно призвано определить факт работоспособности, без акцента на надёжность и другие аспекты. Использование Functional Testing, как правило, мотивируется следующим:

- Уникальная способность обнаруживать ошибки синхронизации, не обнаруживаемые ICT, поскольку он использует номинальные тактовые частоты устройства при тестах.

- Простая спецификация теста, которая уже описана конечной функциональностью платы.

С другой стороны, FT не всегда подходит недостатков:

- Значительные расходы средств и времени из-за методологии тестирования. Иногда необходимо создать уникальное контрольно-измерительное оборудование (HW), а также устройства сопряжения.

- Высокие затраты сил со временем на устранение неполадок сложных плат, поскольку неисправная часть достоверно не определяется.

- Часть дефектов не выявляются, поскольку тестируемое устройство может показать свою работоспособность или, наоборот, неработоспособность только после интеграции в комплекс оборудования, с которым должно взаимодействовать. Примером может оборудование авиационной техники, функциональное тестирование которого выполнимо исключительно в составе общего комплекса авионики.

В нашем мире нет ничего идеального. Нет идеальных вещей, как и людей. А ещё нет идеальной технологии производства продукции со 100% выходом при полном отсутствии брака. Как было сказано в статье ранее, брак — такая же часть производства, как выпуск качественных деталей. Другими словами, он был, есть, будет. Но можно его минимизировать, свести экономические потери от брака к минимуму. Эту цель преследует тестирование печатных плат, призванное как можно раньше выявить неисправность, устранение которой потом стоит уже в 10 раз дороже.

245

245

215

215

415

415